# ВЛИЯНИЕ ОСОБЕННОСТЕЙ ТРАССИРОВКИ В ЦИФРОВЫХ МОДУЛЯХ

Кузин А.А.<sup>1</sup>, Плужников А.Д.<sup>1</sup>, Приблудова Е.Н.<sup>1</sup>, Сидоров С.Б.<sup>1</sup>

<sup>1</sup>ФГБОУ ВПО «Нижегородский государственный технический университет им. Р.Е. Алексеева», Нижний Новгород, Россия (603950, ГСП-41, г. Нижний Новгород, ул. Минина, 24), e-mail: pribludova@nntu.nnov.ru

В статье сформулирована проблема временного рассогласования сигналов мультипроцессорной шины при большой плотности монтажа компонентов. Нестабильность сигналов во времени проявляется в виде редких случайных сбоев, очень трудно поддающихся локализации и устранению, особенно для систем, работающих в широком диапазоне температур. Разработана методика учета особенностей трассировки печатной платы при анализе временных соотношений для сигналов, распространяющихся в быстродействующих цифровых модулях при синхронном обмене данными. Предложено матричное описание задержек распространения сигналов, связанных с различиями в топологии шин адреса/данных/управления системной магистрали и системной синхронизации, сформулирован критерий надежной работы системной шины. Разработанная методика успешно применена для анализа мультипроцессорного кластера на основе отечественных сигнальных процессоров, проектируемого с целью его использования для высокопроизводительной обработки больших объемов информации.

Ключевые слова: мультипроцессорные системы, взаимные задержки, быстродействие, трассировка, синхронный обмен.

#### THE EFFECT OF ROUTE SINGULARITY IN DIGITAL MODULES

### Kuzin A.A.<sup>1</sup>, Pluzhnikov A.D.<sup>1</sup>, Pribludova E.N.<sup>1</sup>, Sidorov S.B.<sup>1</sup>

<sup>1</sup> Nizhny Novgorod State Technical University n.a. R.E.Alekseev, Nizhny Novgorod, Russia (603950, Nizhny Novgorod, street Minina, 24), e-mail: pribludova@nntu.nnov.ru

In the paper problem of time signal error of multiprocessor bus with large density of component wiring is defined. Signal instability to time appear as the occasional random drop-out, very with difficulty yielding localization, debugging and particularly for system working in the long temperature range. Technique of route singularity accounting of printed board with analysis of time relation for signals propagating in high-speed digital modules with synchronous data exchange is devised. The matrix definition of signal dissemination delays concerned with differences in bus topology of address/data/control for the system bus and the system clocking is proposed, safe operation criterion of system bus is defined. Devised technique for the analysis of multiprocessor cluster on basis of home signal processor designed with purpose of the use for advanced processing of the large information volume is applied successfully.

Keywords: multiprocessor systems, relative delay, speed, route, synchronous exchange.

В процессе проектирования современных микропроцессорных систем обычно требуется реализовать одновременное выполнение высоких требований к быстродействию, надежности функционирования и габаритным показателям системы в модульном исполнении. Указанные требования зачастую являются противоречивыми. В частности, уменьшение габаритов аппаратных средств (модуля) усложняет трассировку системной магистрали: оказывается невозможным параллельное размещение всех ее линий на многослойной печатной плате с реальной топологией. В результате задержки сигналов, распространяющихся по различным линиям от одного компонента системы к другому, имеется значительное временное рассогласование. Причем рассогласование проявляется тем более существенно (в смысле понижения надежности из-за случайных сбоев), чем выше требования к быстродействию, приводящие к повышению частоты синхронизации системы. Кроме того, в многопроцессорных системах смена ведущего компонента ведет к такому

изменению задержек сигналов, распространяющихся от этого компонента к ведомым компонентам и в обратном направлении, которое тоже весьма существенно при высоком быстродействии.

По указанным выше причинам возникает необходимость детального анализа проектируемых систем, в частности детального анализа временных соотношений (взаимных задержек) для распространяющихся в них сигналов.

Подобный анализ синхронного обмена проводится, например, в [4], но не учитывает влияние особенностей трассировки системной магистрали и линий системной синхронизации на многослойной печатной плате.

Нашей задачей является уточнение методики анализа временных соотношений для сигналов, распространяющихся в быстродействующих цифровых многопроцессорных модулях при синхронном обмене данными, что позволит избежать грубых ошибок в процессе проектирования.

В соответствии с поставленной задачей проведем анализ временных соотношений в мультипроцессорной системе (МПС) с учетом особенностей трассировки системной магистрали и линий системной синхронизации.

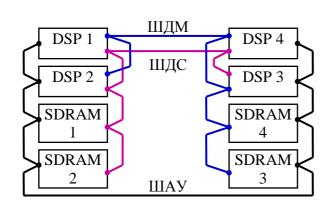

Рис. 1. Схематичная топология МПС

Компоненты мультипроцессорной системы связаны между собой системной магистралью, которая содержит три двусторонние (мультиплексированные) системные шины: шину адреса и управления (ШАУ), шину обмена старшими разрядами (от 63-го до 32-го) данных (ШДС) и шину обмена младшими разрядами (от 31-го до 0-го) данных (ШДМ).

Топология системных шин на печатной плате может существенно различаться, как схематично показано на рис. 1, что приводит к существенному временному рассогласованию

сигналов.

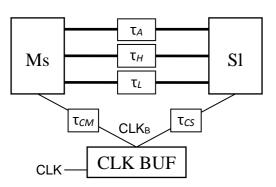

Рис. 2. Схема обмена данными

В мультипроцессорной системе из K подключенных к шине компонентов N могут быть ведущими (Master), т.е. управлять обменом по шине. Смена ведущего (обычно процессора) приводит к перераспределению задержек распространения сигналов от ведущего к ведомым (Slave) и задержек сигналов тактовой частоты.

Синхронный обмен данными по системной магистрали МПС выполнятся по схеме ведущий-ведомый (Master-Slave) или Ms-Sl, как показано на рис. 2. При этом в каждом определенном цикле обмена ведущим является один из процессоров, а ведомым (или ведомыми) — один или несколько из оставшихся компонентов. Следует отметить, что между двумя любыми компонентами МПС существует единственный путь распространения конкретного сигнала.

На рис. 2  $\tau_{A}$ ,  $\tau_{H}$  или  $\tau_{L}$  – задержка (время) распространения сигналов между Ms и Sl по шине ШАУ, ШДС или ШДМ соответственно;  $\tau_{CM}$  – задержка сигнала тактовой частоты от тактового буфера CLK BUF до ведущего компонента;  $\tau_{CS}$  – задержка сигнала тактовой частоты до ведомого компонента.

Очевидно, что  $\mathbf{\tau}_{A}$ ,  $\mathbf{\tau}_{H}$  или  $\mathbf{\tau}_{L}$  (каждая из этих трех величин) определяется трассировкой печатной платы, как детально показано в [1].

Для мультипроцессорной системы блочную матрицу задержек T размера  $N \times K$  (блоков) можно представить:

$$\mathbf{T} = \left| \begin{vmatrix} \mathbf{T_{11}} & \mathbf{T_{12}} & \cdots & \mathbf{T_{1K}} \\ \mathbf{T_{21}} & \mathbf{T_{22}} & \cdots & \mathbf{T_{2K}} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{T_{N1}} & \mathbf{T_{N2}} & \cdots & \mathbf{T_{NK}} \end{vmatrix} \right|,$$

где каждый блок размером 1×3

$$\mathbf{T}_{nk} = \|\mathbf{T}_{Ank} - \mathbf{T}_{Hnk} - \mathbf{T}_{Lnk}\|;$$

$au_{Ank}$  — задержка распространения сигналов по участку ШАУ, которым связаны n-й и k-й компоненты МПС;

$\tau_{Hnk}$  — задержка распространения сигналов по участку ШДС, которым связаны n-й и k-й компоненты МПС;

$au_{Lmk}$  — задержка распространения сигналов по участку ШДМ, которым связаны n-й и k-й компоненты МПС;

k = 1, 2, ..., M;

n = 1, 2, ..., N;

N – количество ведущих компонентов МПС;

K – общее количество компонентов МПС.

C целью упрощения дальнейшего использования в расчетах сформируем блочную матрицу **M** размера  $N \times K$  (блоков):

$$\mathbf{M} = \begin{bmatrix} \mathbf{M}_{11} & \mathbf{M}_{12} & \cdots & \mathbf{M}_{1K} \\ \mathbf{M}_{21} & \mathbf{M}_{22} & \cdots & \mathbf{M}_{2K} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{M}_{N1} & \mathbf{M}_{N2} & \cdots & \mathbf{M}_{NK} \end{bmatrix},$$

где каждый блок размером 1×4

$$\begin{aligned} \mathbf{M}_{nk} &= \|\tau \mathbf{1}_{nk} \ \tau \mathbf{2}_{nk} \ \tau \mathbf{3}_{nk} \ \tau \mathbf{4}_{nk}\|; \\ \tau \mathbf{1}_{nk} &= \max\{\tau_{Ank}, \tau_{Hnk}, \tau_{Lnk}\}. \\ \tau \mathbf{2}_{nk} &= \min\{\tau_{Ank}, \tau_{Hnk}, \tau_{Lnk}\}. \\ \tau \mathbf{3}_{nk} &= \max\{\tau_{Hnk}, \tau_{Lnk}\}. \\ \tau \mathbf{4}_{nk} &= \min\{\tau_{Hnk}, \tau_{Lnk}\}. \end{aligned}$$

Кроме того, опишем блочной матрицей  ${\bf C}$  размера  $1 \times K$  связи CLK BUF с компонентами МПС, реализуемые соответствующими печатными проводниками:

$$\mathbf{C} = \|\mathbf{C}_1 \quad \mathbf{C}_2 \quad \cdots \quad \mathbf{C}_R\|,$$

где каждый блок размером 1×2

$$\mathbf{C}_k = \|\tau_{\min k} \ \tau_{\max k}\|;$$

где  $\tau_{min\ k}$  — минимальная задержка распространения сигнала по печатному проводнику, связывающему буфер CLK BUF с k-м компонентом МПС;

$au_{\max k}$  — максимальная задержка распространения сигнала по печатному проводнику, связывающему буфер CLK BUF с k-м компонентом МПС.

V, наконец, вычислим в соответствии с [1; 5] блочную матрицу **D** размера  $V \times K$  запаса по времени задержки сигналов:

$$\mathbf{D} = \begin{bmatrix} \mathbf{D}_{11} & \mathbf{D}_{12} & \cdots & \mathbf{D}_{1K} \\ \mathbf{D}_{21} & \mathbf{D}_{22} & \cdots & \mathbf{D}_{2K} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{D}_{N1} & \mathbf{D}_{N2} & \cdots & \mathbf{D}_{NK} \end{bmatrix},$$

где каждый блок размером 1×4

$\mathbf{D}_{nk} = \|d\mathbf{1}_{nk} \ d\mathbf{2}_{nk} \ d\mathbf{3}_{nk} \ d\mathbf{4}_{nk}\|;$

$d\mathbf{1}_{nk} = t_{W1} + \tau_{min\ k} - \tau_{max\ n} - \tau \mathbf{1}_{nk}$  – время предустановки для цикла ЗАПИСЬ;

$d2_{nk} = t_{W2} + \tau_{min\;n} + \tau 2_{nk} - \tau_{max\;k}$  – время удержания для цикла ЗАПИСЬ;

$d3_{nk} = t_{R1} + t_{min\ n} - t_{max\ k} - t3_{nk}$  – время предустановки для цикла ЧТЕНИЕ;

$d4_{nk} = t_{R2} + \tau_{min\;k} + \tau 4_{nk} - \tau_{max\;n}$  – время удержания цикла ЧТЕНИЕ;

$t_{W1}$ ,  $t_{W2}$ ,  $t_{R1}$ ,  $t_{R2}$  — временные параметры, не зависящие от трассировки и рассчитанные по методикам [4].

Для надежной работы системной шины элементы матрицы  ${\bf D}$  должны быть неотрицательными.

Изложенная методика оценки временных параметров системной шины с учетом задержек передаваемых сигналов реальными линиями шины применялась в процессе проектирования мультипроцессорного кластера при его реализации на отечественной элементной базе — на базе высокопроизводительных процессоров цифровой обработки сигналов (ВПЦОС), разработанных и производимых в ЗАО «ПКК Миландр» [3].

Принципиальная схема кластера выполнена по структуре, приведенной в [2], внешний вид процессорного кластера показан на рис. 3, топология системных шин схематично показана на рис. 1.

Рис. 3. Внешний вид мультипроцессорного кластера

Кластер содержит четыре процессора ВПЦОС [2] (DSP1-DSP4 на рис. 1), четыре микросхемы синхронной динамической памяти (SDRAM1-SDRAM 4 на рис. 1), загрузочное ПЗУ, тактовый буфер, тактовый генератор и вспомогательные источники питания.

Частота работы системной шины 100 МГц, разрядность данных 64 бита.

Конструктивно мультипроцессорный кластер выполнен на 16-слойной печатной плате размером 80×150 мм (рис. 3), содержит 404 элемента, соединенных 525 цепями.

Особенностью разработанного мультипроцессорного кластера является возможность межпроцессорного обмена данными, когда любой из четырех процессоров (ведущий, Master) имеет доступ к внутренней памяти и регистрам другого (ведомого, Slave) или всех остальных (в режиме широковещательного обмена, Broadcast).

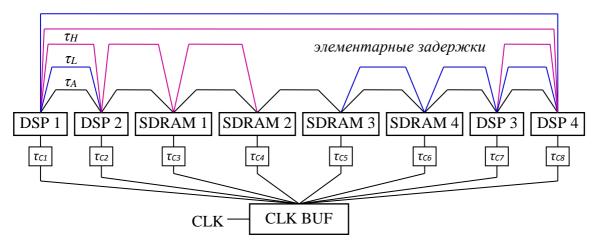

Для расчета и анализа временных задержек с учетом трассировки платы использовалась схема, показанная на рис. 4.

Рис. 4. Схема задержек трассировки

Таким образом, развитая в данной работе методика учета особенностей трассировки при анализе временных соотношений для сигналов, распространяющихся в быстродействующих цифровых модулях при синхронном обмене данными, обеспечивает возможность оценки работоспособности для выбираемых вариантов проектирования.

Работа выполнена при поддержке Министерства образования и науки в рамках договора № 02.G25.31.0061 от 12 февраля 2013 года (в соответствии с Постановлением Правительства Российской Федерации от 9 апреля 2010 г. № 218).

#### Список литературы

- 1. Кузин А.А., Плужников А.Д., Приблудова Е.Н., Сидоров С.Б. Анализ временных соотношений для сигналов в проектируемых цифровых модулях и оценка работоспособности // Цифровая обработка сигналов. 2014.  $\mathbb{N}$   $\mathbb{$

- Сигнальный процессор со статической суперскалярной архитектурой 1967ВЦ2Ф,

К1967ВЦ2Ф,

К1967ВЦ2ФК.

Спецификация.

URL:

http://milandr.ru/uploads/Products/product\_294/spec\_1967VC2.pdf (дата обращения: 29.04.2015).

- 3. ЗАО «ПКК Миландр». Микроконтроллеры и микропроцессоры. 32-разрядные процессоры ЦОС [Электронный ресурс]. Режим доступа:

http://milandr.ru/index.php?mact=Products,cntnt01,default,0&cntnt01hierarchyid=47&cntnt01retur nid=67 (дата обращения: 29.04.2015).

4. Kyle Castille. TMS320C6000 EMIF-to-External SDRAM Interface. Application Report SPRA433E. Texas Instruments, September 2007. - P. 76.

URL: http://www.ti.com/lit/an/spra433e/spra433e.pdf (дата обращения: 30.04.2015).

5. CDCLVC11xx Data Sheet. Texas Instruments, May 2010. - P. 2.

URL: http://www.ti.com/lit/ds/symlink/cdclvc1110.pdf (дата обращения: 30.04.2015).

## Рецензенты:

Хранилов В.П., д.т.н., профессор кафедры компьютерных технологий в проектировании и производстве Нижегородского государственного технического университета имени Р.Е. Алексеева, г. Нижний Новгород;

Флаксман А.Г., д.ф.-м.н., профессор кафедры бионики и статистической радиофизики Нижегородского государственного университета имени Н.И. Лобачевского, г. Нижний Новгород.